Необычный микропроцессор.

Здравствуйте, уважаемые читатели, вы наверное не один раз слышали о разработке мультиклеточного процессора с новаторской архитектурой, при определённых условиях позволяющей распараллеливать выполнение программ между несколькими операционными блоками без участия программиста. При этом, в мультиклеточном процессоре отсутствуют традиционные механизмы, используемые в современных процессорах, такие как конвеер команд, предсказание переходов и устройство неупорядоченного выполнения команд, занимающих существенную часть кристалла современных процессоров.

Производитель мультиклеточных процессоров опубликовал ряд статей с описанием работы мультиклеточного ядра, но у многих читателей количество вопросов по мультиклеточной архитектуре только возросло. Кроме того, принятая разработчиками терминология некоторых читателей сбивала с толку. К сожалению, необычность новаторского метода распараллеливания выполнения программ, стала причиной затруднений в попытках понимания работы мультиклеточного процессора. Поэтому, в этой статье я просто и доступно расскажу об устройстве мультиклеточного процессора и особенностях его работы и программирования, однако, для простоты и понятности, терминология в статье несколько отличается от принятой производителем. В этой статье описывается первый мультиклеточный процессор серии Р1, выпущенный в 2012 году.

Как устроен мультиклеточный процессор?

Устройство процессора.

Мультиклеточный процессор представляет собой процессор с раздельной памятью программ и данных, четырьмя операционными блоками (клетками), буфером результатов, коммутационным устройством для взаимосвязи между компонентами и разбиением программ на пакеты команд. Структурная схема мультиклеточного процессора показана на рисунке:

Ядро процессора может работать на тактовой частоте 100МГц и имеет в своем составе несколько взаимосвязанных блоков.

Процессорные блоки.

Четыре процессорных блока (клеток) (ПБ0-ПБ3), выполняют команды программы. Каждый из процессорных блоков состоит из 32-х битного арифметико-логического устройства с 32-х битным аппаратным делителем и 64-х битным операционным блоком для выполнения арифметических операций с плавающей запятой одинарной точности, а также операций с упакованными и комплексными числами, декодера команд и буфера операндов. Количество процессорных блоков выбрано исходя из возможностей распараллеливания общих задач, при цифровой обработе сигналов можно задействовать до 16 клеток, а обработка видео позволяет одновременно использовать от 64 до 256 клеток.

Память программ.

Каждый процессорный блок имеет по индивидуальному блоку памяти программ объёмом 4Кх64 бит (ПП0-ПП3) для хранения программы. Команды распределяются между процессорными блоками силами компилятора, взаимодействия между отдельными блоками программной памяти нет. Команды из блоков памяти программ выбираются процессорными блоками независимо друг от друга.

Память данных.

Четыре блока оперативной памяти данных объёмом 4Кх64 бит (ПД0-ПД3), хранят данные программы.

Загрузка программ и данных.

Память программ и память данных загружаются из внешней флеш-памяти сразу после сброса процессора. В ходе выполнения программы процессор может изменять содержимое только памяти данных.

Поле регистров.

Четырёхпортовое поле регистров обеспечивает временное хранение информации, косвенный доступ к памяти данных и управление работой процессора. Восемь 64-х битных регистров общего назначения служат для обмена данными между пакетами команд. Шестнадцать 64-х битных индексных регистров предназначены для косвенной адресации к памяти данных. Десять 32-х битных служебных регистров служебные регистры управляют работой ядра процессора. Регистровое поле сделано четырёхпортовым для обеспечения одновременного доступа всех четырёх процессорных блоков к их содержимому.

Периферия.

Периферийные устройства предназначены для обмена информацией между ядром процессора и внешними устройствами. Набор периферийных устройств включает 3 SPI-интерфейса, 4 UART-приёмопередатчика, 2 I2C-интерфейса, по одному контроллеру I2S, Ethernet 10/100/ и USB 1.1, 7 таймеров, часы с календарём, 4 ШИМ,4 порта ввода-вывода и сторожевой таймер. Периферийные блоки имеют 32-битную шину данных и адресное пространство, отображаемое на память данных, то есть записываются и читаются как ячейки оперативной памяти.

Буфер результатов.

Буфер результатов предназначен для временного хранения результатов последних операций и обмена данных между отдельными командами в составе пакета команд. Буфер представляет собой очередь из 64-х штук 64+4 битных ячеек для хранения последних 64-х битных результатов с 4-мя битами признаков операций (флагов). Ёмкость буфера в 64 последних результата выбрана в качестве компромисса между обеспечением распараллеливания программы и сложностью многопортового коммутационного устройства (на самом деле 35 из-за ошибки в процессоре серии Р1, ёмкость буфера не используется полностью, прим. авт.). При выполнении команд, очередь хранящихся результатов сдвигается на число выполненных в текущем такте команд и на освободившиеся ячейки буфера коммутатором записываются результаты только что выполненных команд с 0-го по 3-й операционных блоков, а находящиеся в конце очереди старые результаты выталкиваются из буфера и теряются.

Коммутатор.

Ну и наконец, само сердце мультиклеточного процессора — коммутатор, связывающий воедино все описанные блоки в работающий микропроцессор. Коммутатор представляет собой набор мультиплексоров и сохраняет полученные результаты операций в буфере результатов, обеспечивает одновременный доступ четырёх процессорных блоков к четырём блокам памяти данных и любому из 64-х последних ранее полученных результатов, а также одному из периферийных устройств.

Как мультиклеточный процессор выполняет программу?

Структура программы.

Программы для мультиклеточного процессора состоят не из отдельных команд, а из пакетов команд (параграфов), состоящих из отдельных команд (выражений). По сути, пакет команд воспринимается мультиклеточным процессором как полноценная команда. Пакет представляет собой линейную последовательность команд и имеет один вход (начало) и выход (команда перехода). Запись в регистры и память происходят после выполнения пакета, переходы в программе также происходят между пакетами.

Команды и операнды.

Команды процессора могут быть двухоперандными, однооперандными и безоперандными. Операндом может быть константа (<константа>), содержимое ячейки памяти с явно указанным адресом (<число>), содержимое регистра (#<регистр>), содержимое ячейки памяти, указанное в одном из индексных регистров (#<индексный регистр> или #<индексный регистр>+число) и наконец, ссылка на результат предыдущей команды в буфере коммутатора (@<номер результата относительно текущего 0-го>).

Однооперандные команды могут использовать любой поддерживающийся тип аргумента, двухоперандные команды в качестве первого операнда обязательно используют результат одной из предыдущих операций текущего пакета команд, а безоперандные команды совсем не используют аргументов. Исключение составляет команда установки значений регистров, в которой первым операндом идёт номер регистра (#<регистр>), а второй операнд может быть любым. Также отмечу, что для записи результатов операций в регистр и память используются разные команды.

Форматы данных.

Дополнительно в команде указывается поддерживаемый формат обрабатываемых данных. Операнд может быть числом целым байтовым знаковым/беззнаковым (sb/b), целым четырёхбайтовым знаковым/беззнаковым (sl/l), целым восьмибайтовым (q), четырёхбайтовым знаковым вещественным (f), а также восьмибайтовым знаковый упакованным (p) и восьмибайтовым знаковым комплексным (c), состоящим из двух четырёхбайтовых знаковых вещественных чисел. Однако, не все команды поддерживают все перечисленные форматы данных, например, команда деления может работать только с четырёхбайтовым знаковым вещественным числом.

Выполнение пакета команд.

В первую очередь, процессор переходит к началу очередного пакета команд. Каждый процессорный блок после выполнения предыдущей команды загружает по одной команде из своего блока памяти программ, одновременно загружаются имеющиеся операнды.

Каждый процессорный блок проверяет готовность операндов, и выполняет команду, если все операнды есть в наличии. Если какой-либо из операционных блоков обнаруживает отсутствие необходимого операнда, то выполнение его команды приостанавливается. Наконец, результаты выполненных команд вместе с признаками выполненных операций (флагами) помещаются в буфер результатов коммутатора.

Обращение к сохранённому в буфере результату происходит по его номеру в очереди, начиная с 1-го и заканчивая 64-м. После этого выполняется выборка следующих команд пакета в выполнившие команды операционные блоки. Операционные блоки ожидающие операндов новых команд не выбирают. Цикл выполнения команд начинается заново.

Переходы между пакетами.

При выполнении команд безусловного перехода на следующий пакет команд запоминается его адрес, но выполнение текущего пакета продолжается вплоть до его окончания. При выполении команд записи в регистры и память, запись откладывается до окончания пакета. При выполении команд условного перехода проверяется условие, и если должен быть переход на другой пакет, то далее неиспользуемые следующие команды не загружаются в операционные блоки, а выполнение текущего пакета заканчивается. После выполнения пакета команд, буфер коммутатора полностью очищается, происходит запись в регистры, оперативную память и происходит переход на следующий пакет команд.

Ограничения пакетов команд.

Двухуровневая структура программ выбрана именно для поддержки распараллеливания выполнения команд между процессорными блоками, но она даёт ряд ограничений при написании составляющих программу пакетов команд. Во-первых, выполнение пакетов полностью линейно, ветвления и переходы могут быть только между пакетами, но не внутри них. Во-вторых, запись результатов в регистры и память осуществляются только при окончании выполнения пакета. В-третьих, для записи промежуточных результатов используется именно буфер коммутатора, который полностью очищается после выполнения каждого пакета команд. Такая организация вычислений накладывает некоторые ограничения при написании программ - внутри пакетов не должно быть нескольких команд записи в один и тот же регистр или ячейку памяти данных, нескольких переходов, либо условного перехода с двумя ссылками на один и тот же пакет команд.

Как распараллеливается выполнение программы мультиклеточным процессором?

Распараллеливание программы.

Распараллеливание выполнения программы между процессорными блоками сделано двояко, с одной стороны, разбиением программ на замкнутые пакеты команд, а с другой стороны, распределением команд между процессорными блоками. В описываемом мультиклеточном процессоре задачу распараллеливания команд выполняет компилятор (в следующем мультиклеточном процессоре серии R1 распараллеливание команд осуществляется аппаратно, прим. авт.)

Пример пакета команд.

Рассмотрим пакет команд на примере расчёта площади треугольника по известной формуле Герона. Пусть длины сторон будут заданы в регистрах общего назначения #0, #1, #2, а результат расчёта нужно будет поместить в регистр #3.

Команды 1, 2, 3 загружают исходные данные из регистров общего назначения #0, #1, #2 в буфер результатов. Команда 4 загружает в буфер константу 2 в знаковом формате с плавающей запятой, потому, что в пакете имеются команды деления и извлечения квадратного корня не работающие с другими форматами данных. Команда 5 получает сумму результатов 3-й и 4-й предыдущих команд, а именно складывает загруженные в буфер значения А и В. Команда 6 складывает загруженное 3-й предыдущей командой значение С с полученной 1-й предыдущей командой суммой А и В. Наконец, 7-я команда делит полученный 1-й предыдущей командой периметр на загруженное 3-й предыдущей командой число 2. Команды 8, 9, 10 из полученных результатов расчитывают разности рассчитанного полупериметра и одной из загруженных сторон А, В и С. Команды 11, 12, 13 получают произведение полупериметра на три разности полупериметра и каждой из сторон. Команда 14 задаёт переход на следующий пакет команд, но выполнен переход будет только после выполнения всех команд текущего пакета. Наконец, команда 15 вычисляет квадратный корень из 2-й предыдущей команды, результата всех произведений по формуле. Наконец, команда 16 после окончания пакета команд записывает рассчитанное значение площади треугольника из буфера результатов в регистр общего назначения #3, и происходит переход на следующий пакет next.

Выполнение отдельных команд пакета.

Ход выполнения команд пакета отдельными процессорными блоками показан на рисунке, красным цветом помечены команды, ожидающие отсутствующих в текущем такте операндов:

Первые четыре команды не зависят друг от друга и выполняются одновременно за первый такт.

Во втором такте, пятая команда ссылается на результаты четвёртой и третьей предыдущих команд, то есть первой (5-@4)и второй (5-@3)по порядку команд, поэтому она выполняется. А вот уже загруженная шестая команда приостановлена, так как кроме выполненной предыдущей третьей, то есть третьей(6-@3) по порядку нужен результат первой предыдущей, то есть пятой (6-@1) по порядку команды, поэтому шестая команда во втором такте не выполняется. Седьмая и восьмая команды также приостановлены.

В третьем такте, освободившийся процессорный блок загружает девятую команду, но готов только результат пятой команды и выполняется шестая команда. Седьмая и восьмая команды по-прежнему приостановлены.

В четвёртом такте выполняется седьмая команда и загружается десятая команда пакета. Восьмая, девятая и десятая команды вынуждены опять же ожидать результатов выполнения седьмой команды.

В пятом такте, наконец-то набираются ожидаемые результаты и восьмая, девятая, десятая и свежезагруженная одиннадцатая команды выполняются. Дальнейший ход выполнения команд пакета можно проследить по рисунку самостоятельно.

Ограничения распараллеливания.

На рисунке хорошо прослеживается процесс параллельного выполнения части команд, а также ограничения возможностей параллельного выполения команд. Основное ограничение — это информационная зависимость последующих команд от используемых предыдущих результатов. Нельзя, например, получить сумму, не зная одного из слагаемых. Поэтому, несмотря на выполняемые в среднем почти две команды за такт, в приведённом примере время от времени часть операционных блоков будет простаивать, ожидая результатов выполнения предыдущих команд. Простои операционных блоков, в описываемом мультиклеточном процессоре означают нерациональное использование памяти программ. Причиной является распределение команд между процессорными блоками на этапе компиляции программы и получающихся при этом пробелов в неиспользуемых ячейках памяти:

Например, в описываемом примере используются только 16 из 20-ми ячеек памяти программ, а эффективность использования программной памяти в описывемом примере около 80% (в следующем мультиклеточном процессоре серии R1 использование памяти программ существенно улучшено, прим. авт.).

Как достичь наибольшей производительности мультиклеточного процессора?

Во-первых, при написании пакетов команд следует по возможности избегать использования результатов ближе четвёртого. Иначе будут добавляться такты ожидания выполнения команд соседними процессорными блоками, а также будут появляться неиспользуемые ячейки программной памяти.

Во-вторых, следует избегать одновременного обращения к нескольким ячейкам одного из блоков оперативной памяти данных. Одновременно за один такт можно записать четыре результата в четыре блока оперативной памяти, но запись четырёх результатов в один блок оперативной памяти растянется на четыре такта.

В-третьих, нужно помнить, что порт связи с периферией у коммутатора всего один, и обращение к нескольким регистрам периферийных устойств также даст задержку из-за последовательной отправке пакета данных из коммутатора, каждая посылка также займёт отдельный такт после окончания пакета. Соблюдением вышеописанных условий при написании программ можно получить наибольшую производительность мультиклеточного процессора.

Пути применения мультиклеточного процессора.

Мультиклеточный процессор серии Р1 по организации памяти и набору периферии представляет собой высокопроизводительный микроконтроллер, наиболее подходящий для цифровой обработки сигналов. Четыре операционных блока внутри ядра позволяют выполнять до четырёх команд за такт, буфер результатов сохраняет результаты ряда последних операций, а построение программ из пакетов команд нацелено на поддержку распараллеливания выполнения программы.

Небольшой объём и разделение памяти программ и данных, а также невысокая тактовая частота не позволяет использовать мультиклеточный процессор в качестве универсального процессора персонального компьютера, но возможности распараллеливания выполнения команд и возможности операций с плавающей запятой дают в разы большие возможности цифровой обработки данных по сравнению с другими микроконтроллерами, работающими на равной с мультиклеточным процессором тактовой частоте.

Вычислительной мощности мультиклеточного процессора вполне хватает на обработку оцифрованных звуковых сигналов с последующим шифрованием. Также, благодаря заложенном в мультиклеточном процессоре построении программ на основе пакетов команд, упрощается написание простых интерпретаторов языков программирования высокого уровня. Наконец, мультиклеточный процессор можно использовать в качестве высокопроизводительного микроконтроллера с арифметическим блоком для выполнения ресурсоёмких задач, например, для построения на его основе интеллектуального векторного электропривода для асинхронного электродвигателя.

На этом, уважаемые читатели, я позволю себе откланяться, надеюсь, что мне удалось просто и понятно рассказать вам о мультиклеточном процессоре, о его особенностях, преимуществах и недостатках и доступно ответить многие возникшие вопросы.

На прощание добавлю, что мультиклеточный процессор развивается, в 2015 году был выпущен усовершенствованный мультиклеточный процессор с внешней шиной памяти серии R1, а также в настоящее время разрабатывается новый образец мультиклеточного процессора.

Февраль 2017

Благодарю за внимание, доброго здоровья!

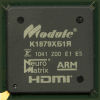

Сайт работает на микрокомпьютере